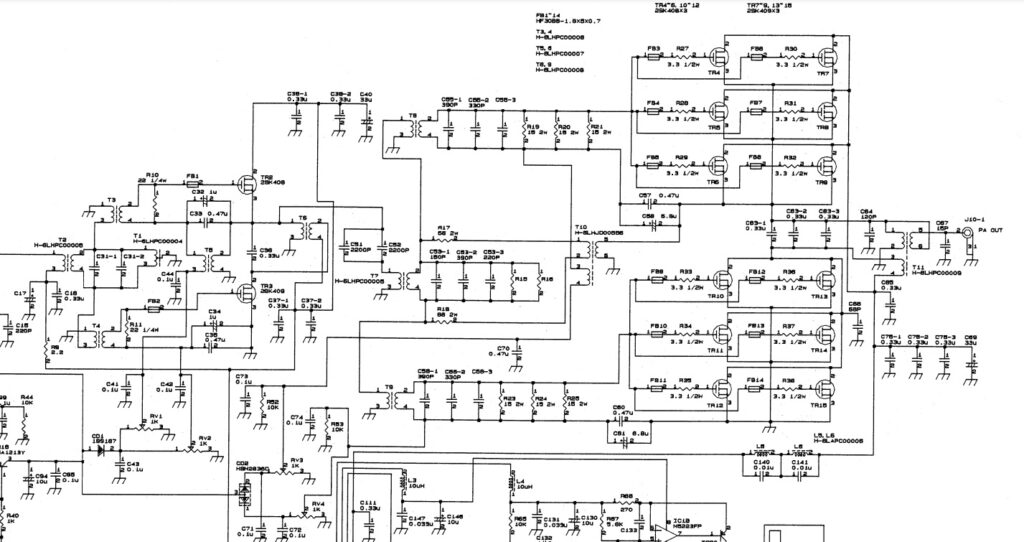

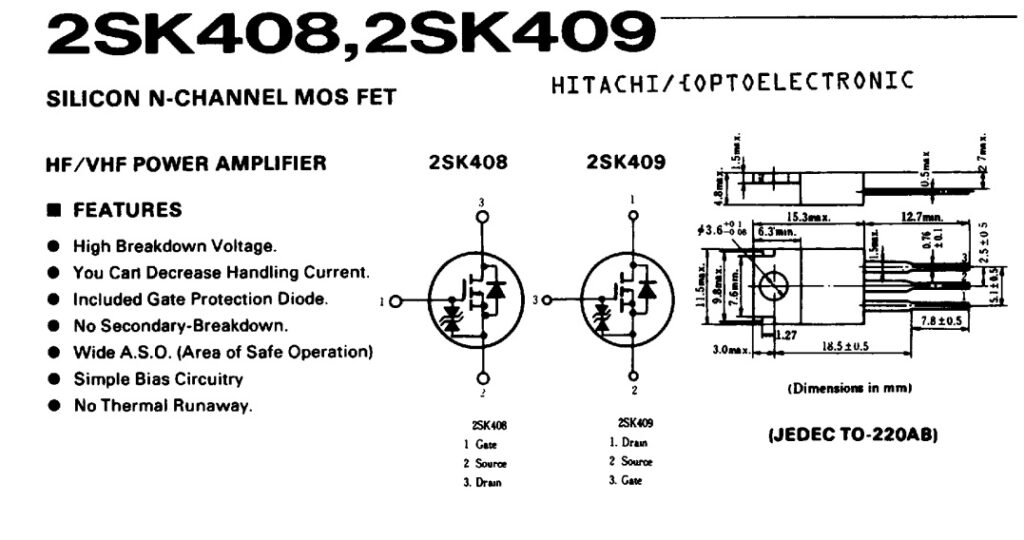

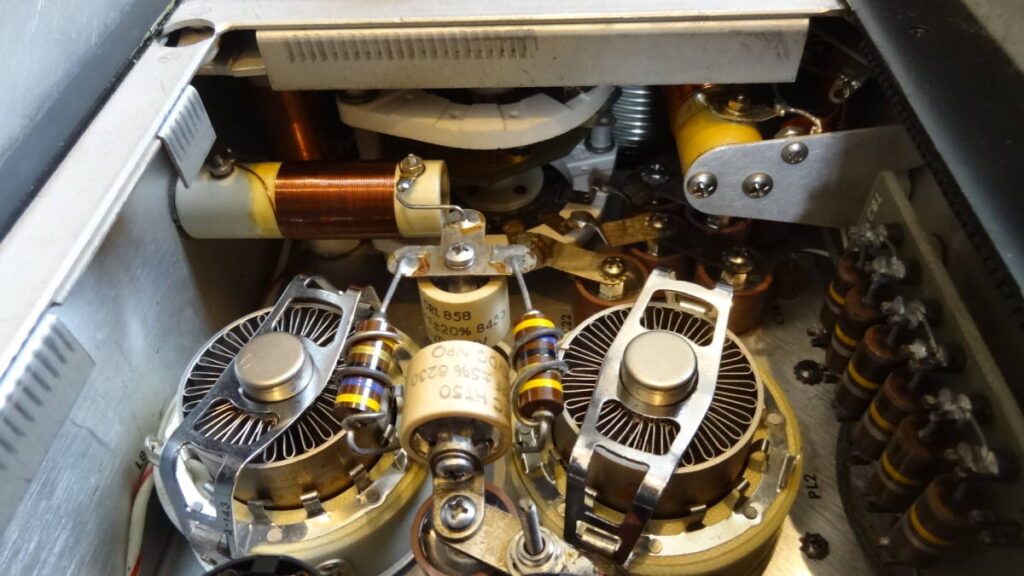

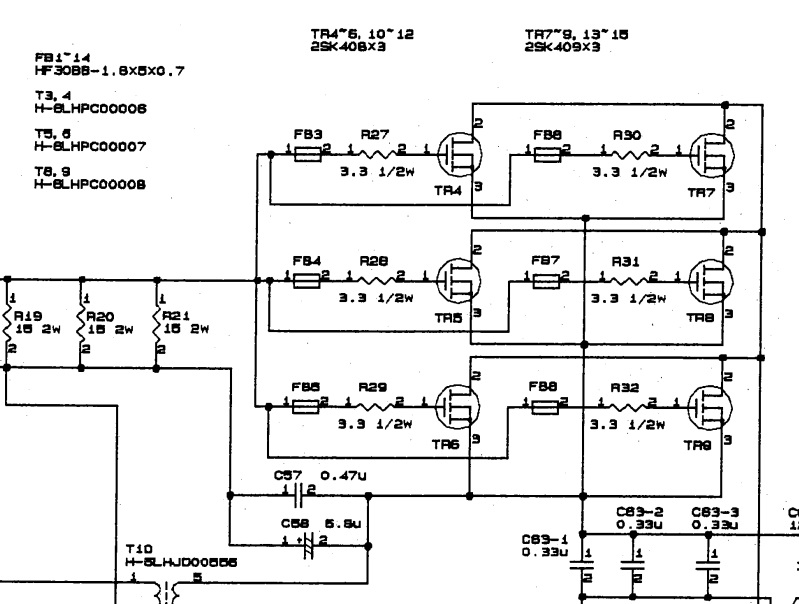

JRC製のJST-245を含むリニア・アンプでは左図の様な2sk408/2sk409を使ったSEPP(Single Ended Push-Pull)回路を用いて低ひずみ率を実現しているようで非常に魅力的な回路構成となっています。

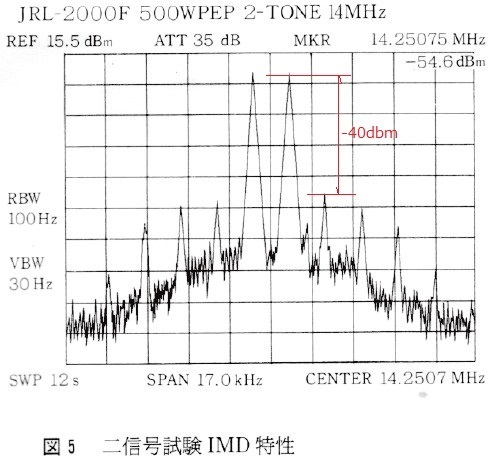

この回路については先般、JA5AUL:今城さんとの交信の際に出て来た話題により興味そそるものがあり、低ひずみ!をどうすれば行えるのか?過去の先駆者達が苦労してきた製品を知ることで身近に利用出来るのではないかと調査し始めました。SEPPと聞けばオーディオ・アンプにて利用されていて身近な回路構成が知られています。一方、JRC製のリニア・アンプではN-Ch MOS FET Deviceを単電源DC+60Vを利用していて回路設計にての工夫されています。驚くのはIMD=-40dbm@500Wと脅威的です。プリディストーションのテクノロジーを利用するとかなり効果的と言えますが、各MOS-FET6個多段並列で使うのは素子単体&モジュールにバラつきがあり覚悟が要ります。最新のテクノロジー・デバイスを利用すれば故障要因やバラつき等も減りますので魅力的とは思います。ローコストのデバイスを使っての中型アンプとして古い・テクノロジーを使って評価したいものです。